1、内存基础

RDRAM(Rambus)、DDR SDRAM甚至是EDO RAM在本质上讲是一样的。RDRAM、DDR RAM、SDRAM、EDO RAM都属于DRAM(Dynamic RAM),即动态内存。所有的DRAM基本单位都是由一个晶体管和一个电容器组成。

上图只是DRAM一个基本单位的结构示意图:电容器的状态决定了这个DRAM单位的逻辑状态是1还是0,一个电容器可以存储一定量的电子或者是电荷。一个充电的电容器在数字电子中被认为是逻辑上的1,而“空”的电容器则是0。电容器不能持久的保持储存的电荷,所以内存需要不断定时刷新,才能保持暂存的数据。电容器可以由电流来充电—当然这个电流是有一定限制的,否则会把电容击穿。同时电容的充放电需要一定的时间,虽然对于内存基本单位中的电容这个时间很短,只有大约0.2-0.18微秒,但是这个期间内存是不能执行存取操作的。

内存至少要每64ms刷新一次,这也就意味着内存有1%的时间要用来刷新。内存自动刷新的关键在于当对内存单元进行读取操作时保持内存的内容不变—所以DRAM单元每次读取操作之后都要进行刷新:执行一次回写操作,因为读取操作也会破坏内存中的电荷,也就是说对于内存中存储的数据是具有破坏性的。所以内存不但要每64ms刷新一次,每次读操作之后也要刷新一次。这样就增加了存取操作的周期,当然潜伏期也就越长。

SRAM,静态(Static)RAM不存在刷新的问题,一个SRAM基本单元包括4个晶体管和2个电阻。它不是通过利用电容充放电的特性来存储数据,而是利用设置晶体管的状态来决定逻辑状态—同CPU中的逻辑状态一样。读取操作对于SRAM不是破坏性的,所以SRAM不存在刷新的问题。

2、SDRAM的结构和功能

内存最基本的单位是内存“细胞”—也就是我们前面展示给大家DRAM基本单元示意图所示的部分,对这个部分通称为DRAM基本单元。每个DRAM基本单元代表一个“位”—Bit(也就是一个比特),并且有一个由列地址和行地址定义的唯一地址。8个比特组成一个字节,它可代表256种组合(即2的八次幂),字节是内存中最小的可寻址单元。

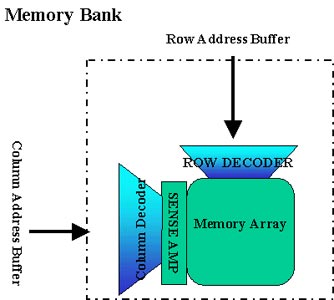

很多DRAM基本单元连接到同一个列线(Row line)和同一个行线(Column line),组成了一个矩阵结构,这个矩阵结构就是一个Bank。大部分的SDRAM芯片由4个Bank组成,而SDRAM DIMM(Dual Inline Memory Module双列直插式)可能由8或者16个芯片组成。SDRAM DIMM有14条地址线和64bit数据线。

每一个内存bank都有一个传感放大器(sense ampplifier),用来放大从基本单元读出(或者写入)内容时电荷。传感放大器根据从芯片组发送来的行地址读出相应的数据,这个读出过程需要一定的时间这就是RAS到CAS的延迟,简称TRCD。不同质量的SDRAM的TRCD需要2或者3个周期。现在已经有了正确的行地址,不过还不知道确切的到那个基本单元去获得信息。CAS延迟时间就是内存用于取得正确的列地址所需要的时间。

注:Latency(延迟)是一种等待的时间,这与内存芯片本身有关。那个C或CAS指的是Column Address Strobe(行地址控制器)。我们不妨将内存想成储存数据的数组、或是表格。为了要确定每个数据的位置,我们会将这些位置以行与列的方式来编号。如此一来,正如所想见的,除了CAS(行地址控制器)以外,还有RAS(列地址控制器)。

内存基本单元就把信号发送到DIMM的输出缓存,这样芯片组就可以读取它们了。现在我们有了前8个字节的内容,以及在传感放大器中有了正确的行地址,等到下面的24个字节的过程就简单了。这时就由内部计数器负责把下一个列地址的内存基本单元的内容发送到DIMM的输出缓存当中。这样每个时钟周期都有8个字节传送到输出缓存中,这种模式就叫做“突发模式”。

主内存的延迟时间(也就是所谓的潜伏期,从FSB到DRAM)等于下列时间的综合:FSB同主板芯片组之间的延迟时间(+/- 1个时钟周期),芯片组同DRAM之间的延迟时间(+/- 1个时钟周期),RAS到CAS延迟时间:RCD(2-3 个时钟周期,用于决定正确的行地址),CAS延迟时间 (2-3 时钟周期,用于决定正确的列地址),另外还需要1个时钟周期来传送数据,数据从DRAM输出缓存通过芯片组到CPU的延迟时间(+/- 2个时钟周期)。

可以看出,一个真正的PC100的SDRAM(CAS=2)的内存取得最前八个字节的时间是9个时钟周期,而另外24个字节只是需要3个时钟周期,这样PC100的SDRAM取得32个字节的数据只是需要12个时钟周期。对于同样的情况,也就是当二级缓存未命中的时候,CPU从内存取得数据所需要的延迟时间需要用如下方法计算:CPU倍频×内存延迟时间=CPU延迟时间。如果500MHZ(5×100MHz)的CPU需要5×9个延迟周期。也就是说如果二级缓存没有命中,CPU需要45个时钟中期才能得到新的数据。

究竟是什么决定DRAM速度?SDRAM是多bank结构,芯片组可以保持一部分曾经访问过的Bank的行地址,也就是说保持一部分已经被打开的“页面”。如果需要访问的数据在同一列中,那么芯片组不需要等待传感器进行变换—这种情况就叫做页面命中。

这时RAS到CAS延迟时间就是0个时钟周期,只需要经过CAS延迟就能在内存缓冲调入正确数据。所以,页面命中就意味着我们只需要等待列地址的确立,就能得到需要的数据了。不过有的情况下,芯片组请求的内存页面不是处于打开的状态,这就叫做页面失效。在这种情况下,RAS到CAS延迟时间将是2或者3时钟周期(根据内存的品质不同而不同)。这种情况就是前面我们讨论过的情形。

如果芯片组已经保持了某一个Bank的某一个行地址,也就是在某一个bank已经打开了一个页面,而请求的数据是位于同一个bank的不同行地址的数据,这种情况是最糟糕的。这样就意味着传感放大器需要首先回写旧的行地址,然后再转换新的行地址。回写旧的行地址所占用的时间叫做“预转换时间”(Precharge time),当遇到这种情况时,是最坏的情况。

这么说可能有点复杂,我们换个简单点的说法:为了要读出或写入某笔数据,内存控制芯片会先传送列的地址,接下来RAS信号就会被激活。然而,在存取行的数据前,还需要几个执行周期才行,这就是所谓的RAS-to-CAS延迟时间。同样的,在CAS信号被执行后,也同样需要几个周期。使用标 准PC133的SDRAM大约是2到3个周期;而DDR RAM则是4到5个周期。在DDR中,真正的CAS延迟时间则是2到2.5个执行周期。

RAS-to-CAS的时间则视技术而定,大约是5到7个周期,这也是延迟的基本因素。你也可以说与CL2.5(DDR)或CL3(SDRAM)比起来,CL2内存更具优势。理论上,这是事实,但还有其它的因素会影响这个数据,例如,新一代处理器的高速缓存较有效率,这表示处理器比较少直接从内存读取数据。再者,列的数据会比较常被存取,所以RAS-to-CAS的发生机率也大,读取的时间也会变多。最后,有时会发生同时读取大量数据的情形,在这种情形下,相邻的内存数据会一次被读取出来,CAS延迟时间只会发生一次。

三、内存的发展历程

起初,电脑所使用的内存是一块块的IC,我们必须把它们焊接到主机板上才能正常使用,一旦某一块内存IC坏了,必须焊下来才能更换,这实在是太费劲了。后来,电脑设计人员发明了模块化的条装内存,每一条上集成了多块内存IC,相应地,在主板上设计了内存插槽,这样,内存条就可随意拆卸了,从此,内存的维修和扩充都变得非常方便。

在80286主板时代的时候,内存条为30pin、256kb,而且必须是由9片颗粒(其中8片为数据位,1片为校验位)组成一个bank(组)。到了486时代内存主要是30PIN SIMM FPM和72PIN SIMM FPM二分天下。FPM RAM也称“快页模式内存”,是用在486及奔腾级计算机的普通内存,为72线,5V电压,带宽为32bit,速度基本都在60ns以上。

EDO(EXTENDED DATA OUT)RAM也称“扩展数据输出内存”与FPM RAM有基本相同的应用范围,有72线和168线之分,5V电压,带宽32bit,速度基本都是40ns以上。由于奔腾及其以上级别的CPU数据总线宽度都是64bit甚至更高,所以EDO RAM与FPM RAM都必须成对使用。

随着时代的发展,Intel发布了Celeron系列处理器以及相关的主板芯片组,内存进入了了SDRAM时代,SD(Synchronous Dynamic)RAM也称“同步动态内存”,都是168线、带宽64bit、3.3V电压,其工作原理是将RAM与CPU以相同的时钟频率进行控制,使RAM和CPU的外频同步,彻底取消等待时间。

伴随着Intel在推出PC100后,由于技术的发展,PC100内存的800MB/S带宽已经不能满足需求,而PC133的带宽提高并不大(1064MB/S),同样不能满足日后的发展需求。此时,Intel为了达到独占市场的目的,与Rambus联合在PC市场推广Rambus DRAM。

Rambus DRAM是Rambus公司最早提出的一种内存规格。它采用了一种和SDRAM不同的架构—新一代高速简单内存架构,基于一种类RISC(Reduced Instruction Set Computing,精简指令集计算机)理论,这个理论可以减少数据的复杂性,使得整个系统性能得到提高。

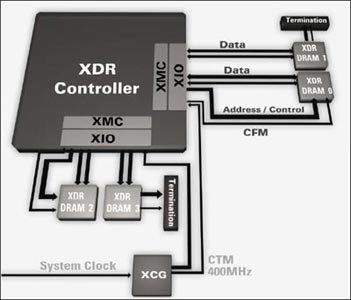

Rambus使用400MHz的16位总线,在一个时钟周期内,可以在上升沿和下降沿同时传输数据,这样它的实际速度就为400MHz×2=800MHz,理论带宽为(16位×2×400MHz/8)1.6GB/s,相当于PC100的两倍。另外,Rambus也可以储存9位字节,额外的一位是属于保留位,可能以后会作为ECC(Error Checking and Correction,错误检查修正)校验。

由于RDRAM的工艺复杂,价格过高,而且Rambus公司还要收取相应的版权收费,再加上闹得沸沸扬扬的i820回收事件。其它厂家出于市场考虑,根据Rambus双向脉冲的特点,提出了DDR SDRAM,也就是我们现在最主流的内存条。

最初DDR内存并未得到Intel的支持,只有少部分使用Athlon处理器的芯片组才支持,但是随着市场的扩大,Intel也渐渐的按捺不住,这种焦急在威盛电子推出P4X266芯片组后终于爆发,推出了Intel使用DDR内存的第一种P4芯片组—i845D。严格说来,直到这个时候,Intel还没有完全抛弃支持RDRAM内存的i850芯片组。

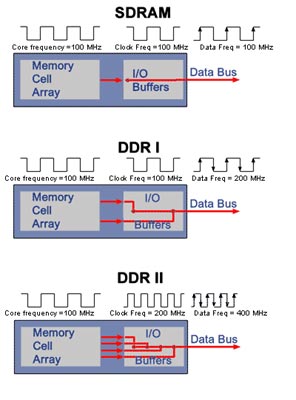

DDR SDRAM(Dual Date Rate SDRAM)简称DDR,也就是“双倍速率SDRAM“的意思。DDR SDRAM也可以说是传统SDRAM的升级版本,最重要的改变是在数据传输界面上。

DDR在时钟信号上升沿与下降沿各传输一次数据,这使得DDR的数据传输速度为传统SDRAM的两倍。由于仅多采用了下降缘信号,因此并不会造成能耗增加。至于定址与控制信号则与传统SDRAM相同,仅在时钟上升缘传输。

它另一个明显的改变就是增加了一个双向的数据控制接脚。当系统中某个控制器发出一个写入命令时,一个DQS信号便会由内存控制器送出至内存。而传统SDRAM的DQS接脚则用来在写入数据时做数据遮罩同步传输,不会有某个人数据传输较快,而有些数据传输较慢的情况。 随着Intel新一代芯片组—i915/925的发布,我们又迎来了内存的又一个“春天”,DDR II。

DDR-II内存将是现有DDR-I内存的换代产品,它们的工作时钟预计将为400MHz或更高。从JEDEC组织者阐述的DDR-II标准来看,针对PC等市场的DDR-II内存将拥有400-、533、667MHz等不同的时钟频率。

高端的DDR-II内存将拥有800-、1000MHz两种频率。DDR-II内存将采用200-、220-、240-针脚的FBGA封装形式。最初的DDR-II内存将采用0.13微米的生产工艺,内存颗粒的电压为1.8V,容量密度为512MB。

DDR-II将采用和DDR-I内存一样的指令,但是新技术将使DDR-II内存拥有4到8路脉冲的宽度。DDR-II将融入CAS、OCD、ODT等新性能指标和中断指令。DDR-II标准还提供了4位、8位512MB内存1KB的寻址设置,以及16位512MB内存2KB的寻址设置。DDR-II内存标准还包括了4位预取数(pre-fetch of 4 bits)性能,DDR-I技术的预取数位只有2位。

结语:

纵观以上的内存历史,我们看到从最早只能达到30ns、256KB的内存条到SDRAM一统天下,延续到现今内存主流DDR I,而现如今DDR II也浮出水面,还有尚未尘埃落定的QBM内存,时代的发展促进着计算机技术的不断进步,处在这个技术飞速发展的年代,未来也许还有更多的精彩。